Table des matières

Les familles logiques

Introduction

Une fonction logique peut être réalisée avec différentes technologies dont les caractéristiques varient (tensions, courants, temps de propagation, etc.).

Logique positive ou négative

En logique positive : “0” (niveau logique bas) ↔ V- et “1” ↔ V+ (niveau logique haut)

En logique négative : “0” (niveau logique bas) ↔ V+ et “1” ↔ V- (niveau logique haut)

V- : la tension la plus faible V+ : la tension la plus élevée

Notation

VOH : Tension de sortie (Out) à l'état haut (High)

VOL : Tension de sortie (fut) à l'état bas (Low)

VIH : Tension d'entrée (In) à l'état haut (High)

VIL : Tension d'entrée (In) à l'état bas (Low)

IOH : Courant de sortie (Out) à l'état haut (High)

IOL : Courant de sortie (Out) à l'état bas (Low)

IIH : Courant d'entrée (In) à l'état haut (Low)

IIL : Courant d'entrée (In) à l'état bas (High)

Caractéristiques statiques

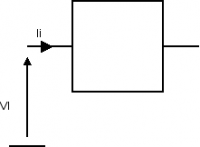

Caractéristique d'entrée

VI=f(II)

Permet de déterminer VILmax et VIHmin (tension d'entrée à l’état bas max, tension d'entrée à l’état haut min)

Caractéristique de sortie

On en définit deux :

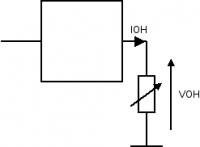

Sortie à l'état haut :

VOH=f(IIOH)

Permet de déterminer VOHmin (tension de sortie à l'état haut min)

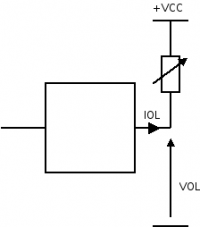

Sortie à l'état bas :

VOL=f(IIOL)

Permet de déterminer VOLmax (tension de sortie à l'état bas max)

Entrance (Fan-in)

Elle donne la consommation d'une entrée par le nombre d'entrées de la porte de référence équivalente.

FI>II/IIref

Sortance (Fan-out)

Elle correspond au nombre d'entrée élémentaire que peut alimenter la porte.

FO<IO/IIref

Ces deux facteurs sont définis pour l'état haut et l'état bas. Ils sont en général différents on prendra dans chaque cas le plus défavorable.

FI=MAX(FIL,FIH);FO=MIN(FOL,FOH)

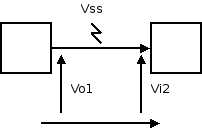

Immunité au bruit

Lorsque 2 portes sont reliées, il peut exister une tension parasite Vss se rajoutant à Vo1 (Vi2=Vo1+Vss), par exemple , par induction dans le fil les raccordant.

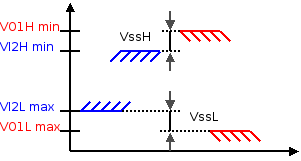

Immunité statique

Lorsque la durée de la tension parasite dépasse le temps de propagation dans la porte (tp), on définit la marge de bruit par la valeur maximale de la tension Vss qui n'influe pas sur l'état de sortie.

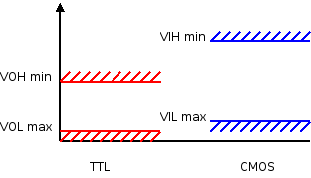

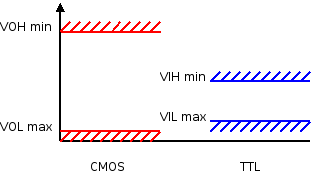

VssL = VIL max - VOL max

VssH = VOH min - VIH min

Il faut donc que VOH > VIH et VOL < VIL

Immunité dynamique

Caractéristiques dynamiques

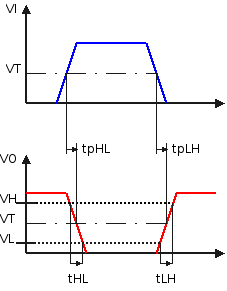

Une porte logique ne commute pas instantanément lorsque son entrée évolue d'un état logique à l'autre.

tLH : Temps de montée tHL : Temps de descente tpHL et tpLH : Temps de propagation

Le temps de propagation moyen est définit par tp=(tpHL+tpLH)/2 Il impose la durée de l'impulsion minimum de commande et de la fréquence maximale de travail d'un circuit.

Consommation et facteur de mérite

Les constructeurs indiquent pour une tension d'alimentation (VCC) le courant consommé lorsque toutes les portes sont à l'état bas (IccL) ou à l'état haut (IccH). Il donne également la puissance consommée par la porte (Pd) ainsi que le facteur de mérite tpxPd (nS,mW) qui chiffre les performances d'une porte.

Technologie TTL

La technologie TTL (Transistor Transistor Logic) est la 1ere grande technologie qui s'est généralisée dans la fabrication de circuits intégrés. Elle est apparue dans les années 60.

Les sous familles TTL qui en ont découlé :

| TTL | ||

| TTL-L | Low Power | devenue obsolète |

| TTL-H | High Speed | devenue obsolète |

| TTL-S | Schottky | |

| TTL-LS | Low Power Schottky | |

| TTL-ALS | Advanced Low Power Schottky | Nouvelles technologie |

| TTL-AS | Advanced Schottky | Nouvelles technologie |

| TTL-FAST | Advanced Schottky | Nouvelles technologie |

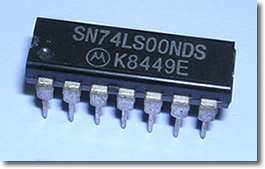

Marquage

xx(1) 74/54(2) xxx(3) xxx(4)

(1) : marquage constructeur SN,F, etc

(2) : 74: série commerciale (0° à 70°C) / 54: série militaire (-55° à 125°C), définit la plage de température de fonctionnement

(3) : Sous-famille (S,LS,etc)

(4) : Référence de la fonction

ex : 74LS00 Porte NAND à deux entrées (00) de la technologie TTL/LS

Schéma interne

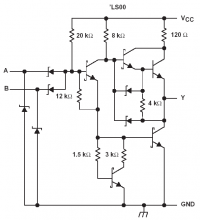

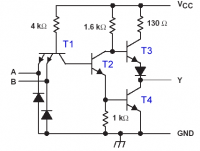

Structure interne d'une porte NAND standard:

Le potension le plus élevé de l'alimentation s'appelle VCC et le plus bas GND.

T1 : Réalise la fonction logique OU

T3 et T4 : Sortie “Totem-Pole”

Structure interne d'une porte NAND LS:

Valeurs caractéristiques

| TTL Standard | TTL LS | ||

|---|---|---|---|

| Vcc | 5V +/- 5% | Vcc | 5V +/- 5% |

| VIH min | 2V | VIH min | 2V |

| VIL max | 0.8V | VIL max | 0.8V |

| VOH min | 2.4V | VOH min | 2.7V |

| VOL max | 0.4V | VOL max | 0.5V |

| IIL max | -1.6mA | IIL max | 0.4mA |

| IIH max | -40µA | IIH max | 20µA |

| IOL max | 16mA | IOL max | 8mA |

| IOH max | 0.8mA | IOH max | -0.4mA |

| temps de propagation | 10ns | temps de propagation | 9.5ns |

| Puissance consommée/porte | 10nW | Puissance consommée/porte | 2nW |

| Sortance H | 20 UL | Sortance H | 20 UL |

| Sortance L | 10 UL | Sortance L | 20 UL |

Utilisation pratique

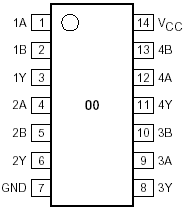

Le “haut” du circuit intégré est indiqué par une marque ( ou détrompeur), ici un rond. La 1er patte en haut à gauche et toujours la patte 1. Les pattes d'alimentation VCC et GND sont généralement à l'opposé l'une de l'autre et GND est du coté de la patte 1.

Technologie CMOS

CMOS (Complementary Metal Oxide Semi-conducteur): cette technologie utilise des transistors MOS à canal N et canal P.

Actuellement le marché des circuits intégrés numérique montre une forte croissance des circuits CMOS au détriment des circuits TTL.

| CMOS | ||

| 4000 | Alimentation 3 à 18V | devenue partiellement obsolète |

| 45… | Alimentation 3 à 18V | |

| 74C | Brochage compatible TTL | devenue obsolète |

| 74HC | 74C Haute vitesse | |

| 74HCT | 74HC à niveau compatible TTL | |

| 74AC | 74 Advanced C | Travail à des fréquences très élevées |

| 74ACT | 74 Advanced CT | Travail à des fréquences très élevées |

| 74LV | 74 Low Voltage - Alimentation 2.7 à 3.6V | |

| 74ACT | 74 Low Voltage C - Alimentation 2 à 3.6V | Travail à des fréquences très élevées |

Marquage

Pour la série 4000: xx(1) 4xxx(2) x(3) x(4) xx(5)

(1): Préfix CD (Harris Digital Logic IC)

(2): Référence de la fonction

(3):

- A: VDDmax = 12 V

- B: VDDmax = 18 V

- UB: B Unbuffered (sorties non amplifiées)

(4): Type de boîtier

- D: Ceramic Side-Brazed Dual-In-Line Package (DIP)

- E: Plastic DIP

- F: Ceramic DIP

- K: Ceramic Flatpack

- M: Plastic Surface-Mount Small-Outline Integrated Circuit (SOIC)

- SM: Plastic Shrink SOIC (SSOP)

- M96: Reeled Plastic Surface-Mount SOIC

- SM96: Reeled Plastic Shrink SOIC (SSOP)

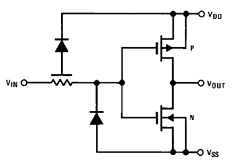

Schéma interne

Exemple d'une porte inverseuse:

Le potension le plus élevé de l'alimentaiton s'appelle VDD et le plus bas VSS.

Les diodes permettent d'éviter les tensions supérieures à VDD. La résistance permet de faire chuter la tension qui est appliquée aux grilles des transistors.

Ve='1'→ TN conduit et TP bloqué → VS='0'

Ve='0'→ TN bloqué et TP conduit → VS='1'

Valeurs caractéristiques

Tension d'alimentation

La plage d'alimentation de la série 4000 est de 3 à 18V. Les nouvelles générations, qui sont compatibles avec la technologie TTL, 74HC, HCT, n'autorisent que des tensions comprises entre 2 et 6V.

Niveau de tension

Le changement d'état de la sortie se traduit lorsque la tension d'entrée passe par une valeur proche de Vcc/2.

On a, approximativement :

- VOH = Vcc

- VOL = 0V

- VIH min = 70% Vcc

- VIL max = 30% de Vcc

Caractérisique d'entrée

La résistance d'entrée est très élevée (>1010 ohms) donc l'intensité d'entrée est négligeable en pratique.

Caractérisique de sortie

Le courant de sortie ne doit pas dépasser 10mA pour les circuits classiques que se soit à l'état haut ou bas.

Immunité au bruit

La marge d'immunité au bruit dépend de la tension d'alimentation.

VssL = VIL max - VOL max

VssH = VOH min - VIH min

Mais on peut quand même remarquer que plus la tension d'alimentation augmente plus la marge d'immunité au bruit augmente. Si on se fixe en tension d'alimentation, comme 5V, pour comparer à la famille TTL, on remarque que la marge d'immunité au bruit des CMOS (1.5V) est plus élevé que pour les TTL (0.4V)

Puissance consommée

Exemples:

En statique :

VDD = 5V P = 2.5nW, consommation faible, proche de la technologie TTL LS

VDD = 10V P = 10nW

En dynamique : Le courant consommé et par conséquence la puissance. Cf Datasheet.

Sortance

En statique : La sortance est très élevée, supérieur à 100UL.

En dynamique : La sortance peut passer à 10 ou 15UL dans certains cas (fréquence élevée, technologie HCT)

Temps de propagation

Exemples:

VDD = 5V Tp=35nS On remarque que le temps de propagation des CMOS est approximativement 3 fois plus important que celui des TTL.

VDD = 10V Tp=25ns On remarque que le temps de propagation diminue avec l'augmentation de la tension d'alimentation.

Cette différence s'amenuise, voir s'inverse, avec les dernières technologies CMOS HC ou AC.

Utilisation pratique

Les entrées CMOS non utilisées ne doivent pas être laissées en l'air. Le potentiel de ces entées n'étant pas fixes, les transistors commandés peuvent prendre n'importe quel état, ce qui entraîne une consommation inutile. Le niveau appliqué à ces entrées n'a pas d'importance 0V ou VDD.

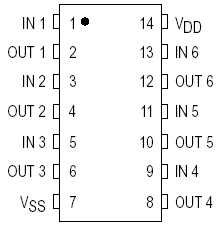

Le “haut” du circuit intégré est indiqué par un détrompeur, ici un rond. La 1er patte en haut à gauche et toujours la patte 1. Les pattes d’alimentation VDD et VSS sont généralement à l’opposé l’une de l’autre et VSS est du coté de la patte 1.

Comptabilité des technologies

Vu les différences entre les caractéristiques électrique des différentes familles, il faut prendre un certain nombre de précautions lorsqu'on veut utiliser ensemble des portes TTL et CMOS.

TTL vers CMOS

Il n'y a pas compatibilité sauf si la porte CMOS est du type HCT (Compatible TTL)

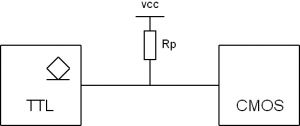

La solution la plus simple pour remédier à ce problème est de rajouter une résistance de rappel (ou tirage). On peut aussi utiliser une porte TTL à sortie à collecteur ouvert. La résistance de rappel se calculera dans la même manière. Une autre solution consiste à d'intercaler une porte HCT entre la TTL et la CMOS.

INTERFACAGE

74HCT

Sortie à collecteur ouvert

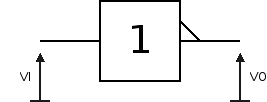

La sortie à collecteur ouvert est représentée par le symbole : ![]()

L'étage de sortie correspond à :

L'adaptation se fait grace à une résistance de tirage Rp :

Calcul de Rp

Une valeur trop grande de Rp diminuera la fréquence maximale d'utilisation et un valeur trop petite augmentera la puissance dissipée.